应用材料公司推出了一种全新的先进逻辑芯片布线工艺技术,可微缩到3纳米及以下技术节点。

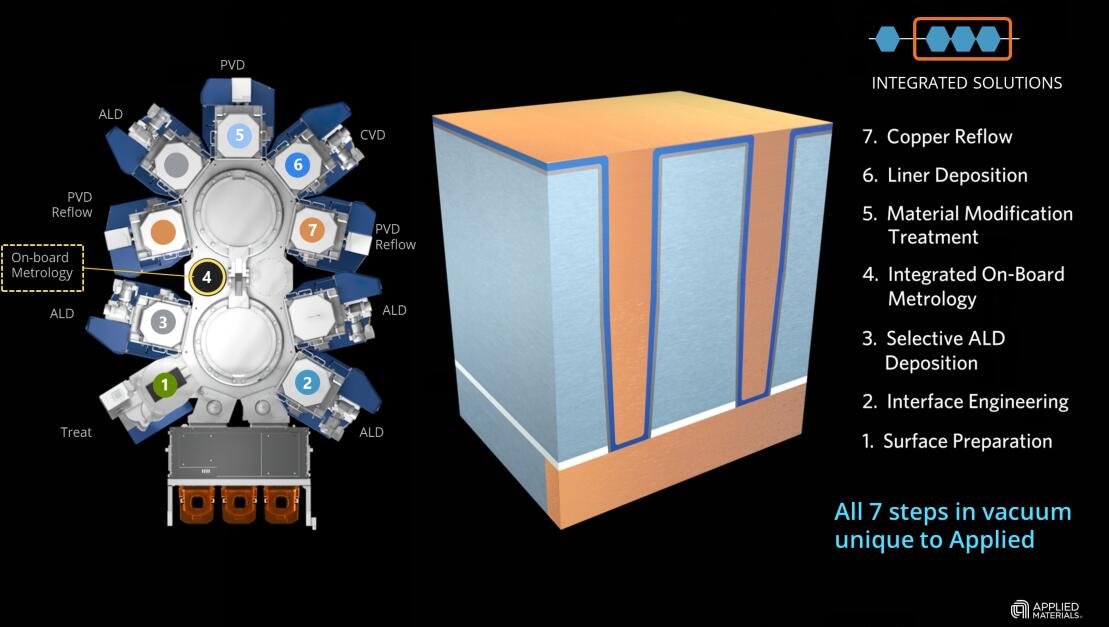

应用材料公司全新的Endura Copper Barrier Seed IMS解决方案在高真空条件下将七种不同工艺技术集成到了一个系统中,从而使芯片性能和功耗得到改善。

虽然晶体管尺寸缩小能够使其性能提升,但这对互连布线中的影响却恰恰相反:互连线越细,电阻越大,导致性能降低和功耗增加。从7纳米节点到3纳米节点,如果没有材料工程技术上的突破,互连通孔电阻将增加10倍,抵消了晶体管缩小的优势。

应用材料公司开发了一种名为Endura? Copper Barrier Seed IMS?的全新材料工程解决方案。这个整合材料解决方案在高真空条件下将ALD、PVD、CVD、铜回流、表面处理、界面工程和计量这七种不同的工艺技术集成到一个系统中。其中,ALD选择性沉积取代了ALD共形沉积,省去了原先的通孔界面处高电阻阻挡层。解决方案中还采用了铜回流技术,可在窄间隙中实现无空洞的间隙填充。通过这一解决方案,通孔接触界面的电阻降低了50%,芯片性能和功率得以改善,逻辑微缩也得以继续至3 纳米及以下节点。

应用材料公司高级副总裁、半导体产品事业部总经理珀拉布?拉贾表示:“每个智能手机芯片中有上百亿条铜互连线,光是布线的耗电量就占到整个芯片的三分之一。在真空条件下整合多种工艺技术使我们能够重新设计材料和结构,从而让消费者拥有功能更强大和续航时间更长的设备。这种独特的整合解决方案旨在帮助客户改善性能、功率和面积成本。”

Endura Copper Barrier Seed IMS系统现已被客户运用在全球领先的逻辑节点代工厂生产中。有关该系统和其它逻辑微缩创新的更多信息已在美国时间6月16日举行的应用材料公司 2021逻辑大师课上进行了讨论。